Course Flyer [PDF]

We are Microdevice Technologies, Mumbai. We are the sole exclusive authorized training partners of SafeTTy Systems. We are authorized to conduct training using the technology developed by SafeTTy Systems for which they hold patents in the broader field of the design of safety critical embedded systems using C-programming language.

Brief of SafeTTy Systems Ltd

From their base in the UK Midlands, they provide support for organisations across the world that need to create real-time embedded systems that are safe, reliable and secure.

Many of their customers need to achieve compliance with IEC 61508, ISO 26262, DO-178 and related international safety standards and guidelines. They help them to meet these requirements through the use of state-of-the-art “Time-Triggered” (TT) software architectures.

To support their customers, they offer:

- specialised consultancy services;

- a range of training courses with an associated staff certification programme;

- flexible ReliabiliTTy® Technology Licences;

- a range of DuplicaTTor® Boards and related support packages;

- a series of popular books on TT systems and functional safety, including the recently-published ‘ERES2‘.

Who is behind SafeTTy Systems..

The team at SafeTTy Systems Ltd is led by Dr Michael J. Pont CEng.

Michael was awarded a BSc degree (in Electronics and Electrical Engineering) by the University of Glasgow (UK) and a PhD (in Computer Science) by the University of Southampton (UK). He is the author of several successful books and more than 100 technical papers: he is named inventor / co-inventor on a number of patents and patent applications.

Michael has been working in the field of time-triggered (TT) embedded systems for more than 20 years. He has helped numerous companies to create successful TT designs. Many of these designs have been produced in compliance with international safety standards and guidelines (including IEC 61508, ISO 26262 and DO-178).

Michael began this work on TT systems in the academic sector, latterly as Professor of Embedded Systems Engineering at the University of Leicester (UK). In Leicester, Michael established the Embedded Systems Laboratory, invented the PTTES “pattern language”, and led teams that developed the “NISA” safety agent, and the first single- & multi-core processors that were designed specifically to run TT software. During his time with the University of Leicester, Michael supervised more than 20 successful PhD projects.

In order to commercialise some of the above technology, Michael founded and served as CEO of the University of Leicester “spin out” company TTE Systems Ltd.

Michael currently serves as CEO of SafeTTy Systems Ltd (January 2014 – date).

What technology is owned by SafeTTy Systems

They have developed technology that is licensed to customers through their ReliabiliTTy® programme.

This technology includes the following patents:

- Pont, M.J. (2016) “A monitoring unit as well as method for predicting abnormal operation of time-triggered computer systems”, SafeTTy Systems Ltd, GB2526082.

- Pont, M.J. (2016) “A framework as well as method for developing time-triggered computer systems with multiple system modes”, SafeTTy Systems Ltd, GB2526083.

Related international patents have been applied for.

What Trademarks are owned by SafeTTy Systems..

AcquisiTTor, ConnecTTor, CorrelaTTor, DecomposiTTor, DisrupTTor, DuplicaTTor, MoniTTor, PredicTTor, RapidiTTy, ReliabiliTTy, SafeTTy, SafeTTy Certified, SafeTTy Systems, TriplicaTTor, TTE and WarranTTor are registered trademarks or trademarks of SafeTTy Systems Ltd in the UK and other countries.

What is the SafeTTy Certified training programme..

The SafeTTy Certified programme is designed to help people obtain the skills needed to develop safe, reliable and secure embedded systems using TT architectures – and provide evidence that they possess such skills.

The programme starts at “Level 0” and progresses to “Level 2”

In our view:

- Level 0 represents the foundation level qualification that should be expected from an individual desirous of learning the art of developing real-time embedded systems.

- Level 1 represents the minimum qualification level that should be expected from an individual involved in the development of real-time embedded systems that are intended to be reliable, but where failure has no direct safety implications.

- Level 2 represents the minimum qualification level that should be expected from an individual involved in the development of real-time embedded systems that may have some safety implications (for example, designs developed in compliance with IEC 61508 or in compliance with ISO 26262), and / or where system failure could prove very expensive (e.g. deep-sea products, satellite systems).

Various Courses offered under the SafeTTy Certified Track

Course Name: Level-0 Embedded C (EC)

Course Location: On-Campus

Course delivery: Face-to-face on-campus delivered by our internationally certified trainer.

Course Duration: 60hrs (4hrs. per day), conducted as per the convenience of the institution.

Benefits for the course participants: Every participant will get a TI MSP432 launchpad kit along with Code Composer Studio. Course delivered on-campus. Internationally designed Courseware which is the copyright of SafeTTy Systems(UK) designed by Dr. Michael J. Pont. Course focuses on the design aspects with Time Triggered architecture and not Event Triggered(Interrupt driven) architecture which is generally followed in engineering courses. Internationally recognized Certificate will be awarded to successful candidates at the end of the course by SafeTTy Systems UK. Course is mapped to regular course curriculum using ARM Cortex M4 microcontroller. Further course levels are available for further study to craft a career in embedded systems domain. International Certificate for Level-0 from SafeTTy Systems.

Key features of this course

- A consistent focus on designing code that is safe and reliable.

- Course begins with the study of ARM architecture.

- A crash course on ‘C’ is included in the course itself, in case your skills are a little rusty.

- Creating a Simple Embedded OS; this is the starting point in learning about TT architectures.

- Learning about a single interrupt approach to carry out different tasks.

- Internationally-recognized certificate provided for successful candidates.

Course Objectives

After completing the course, participants should:

- Understand ARM architecture

- Use features of ‘C’ to create structured embedded code.

- Write code that is reliable and responsive.

- Be comfortable with designing code that adheres to timing constraints.

- Understand the necessity of an Embedded OS.

- Understand the ‘One Interrupt per Microcontroller Rule’ in the design of TT systems.

- Understand the basic building blocks of TT architecture.

- Be ready to go to the next certification level LEVEL 1.

Prerequisites

Familiarity with Windows OS, good knowledge of binary number system and digital electronics. Familiarity with ‘C’ language would be an advantage.

Syllabus

- Overview of ARM architecture.

- Memory map of the ARM Cortex-Mx microcontroller.

- Timers of MSP432.

- Machine cycle and oscillator frequency calculations.

- SysTick Timer and its use in an Embedded OS

- Crash Course on C programming with focus on loops, functions, function prototypes, variable declaration and definition , pointers , typedefs , macros ,unsigned numbers .

- CCS environment.

- Creating project, building the target and running the code on target board.

- Understanding Energy trace in CCS.

- Reading Switches,Controlling Multi-colored LED

- Structuring Code and Object Oriented programming with C.

- Real Time constraints

- Creating a small Embedded OS.

- Multistate systems and function sequences.

- Generating PWM signal.

- Traffic signal system using FSM.

- Watchdog timer and their use in recovery from failure.

- Serial Port programming of MSP432.

Mode of assessment for CERTIFICATION

- Closed book exam with university-style conditions.

- Planned exercises that would be submitted by candidates during the course.

Certification

- On successful completion of the course candidates will receive LEVEL 0 internationally recognized Certification from SafeTTy Systems.

Course duration and delivery

- Course duration is 60 hrs. (4hrs. per day).

- Course lectures will be held as per the convenience of the institution.

- Candidates are expected to complete 5 practical exercises .To be submitted during the course.

- Exercises carry weightage towards final certification.

- Final written examination of 2 hours’ duration would be conducted on completion of the course.

- Successful candidates will receive SafeTTy Certified certificates within 2- months of successful course completion.

Course Name: Level-1 Foundations of Reliable Embedded Systems(TTa)

Course Location: On-Campus

Course delivery: Face-to-face on-campus delivered by our internationally certified trainer.

Course Duration: 8-weeks, as per the convenience of the institution.

Benefits for the course participants: Course delivered on-campus. Internationally designed Courseware which is the copyright of SafeTTy Systems(UK) designed by Dr. Michael J. Pont. Course focuses on the design aspects with Time Triggered architecture and not Event Triggered(Interrupt driven) architecture which is generally followed in engineering courses. Internationally recognized Certificate will be awarded to successful candidates at the end of the course. Course focuses on CPU schedulers. Further course levels are available for further study to craft a career in embedded systems domain. International Certificate for Level-1 from SafeTTy Systems.

Key features of this course

- A consistent focus on the creation of reliable embedded systems in a wide range of sectors.

- Provides an introduction to modern Time-Triggered (TT) system architectures.

- Provides a solid foundation for people interested in the development of safety-related systems.

Course Objectives

- After completing the course, participants should:

- Understand the key concepts of “real-time” systems and the importance of timing behavior when creating reliable embedded systems.

- Understand key design and programming techniques which can help to improve the reliability of embedded systems for use in a range of different market sectors.

- Understand time-triggered (TT) software architectures.

- Understand how to test and debug existing embedded systems.

- Be ready for more advanced training in software design and system verification and progress to LEVEL 2.

Prerequisites

- Level 0 Certification or Experienced Professionals wishing to learn about TT architectures.

Syllabus

- What is an Embedded and a Deeply Embedded System.

- Discussion on 8051 architecture.

- Why use C?

- Difference between writing code for desktop and an embedded system and the differences in their software architecture.

- What are TASKS?

- What is a Real Time Embedded System?

- Accuracy of Loop Delays and Hardware Delays.

- What are Sandwich delays and why do we use them?

- What are timeout mechanisms and why and when do we need to timeout?

- What is the concept of balanced code?

- Concept of Worst Case Execution Time (WCET) and Best Case Execution Time (BCET) of Tasks.

- Understanding Interrupts and Interrupt response time.

- Understanding TT embedded operating system.

- Explore Co-operative and Hybrid schedulers and why we need them and when to employ them.

- How to handle Task Jitter?

- Timing analysis of tasks

- Compare 8-bit 8051, 32- bit ARM, soft processor implemented on FPGA and x86 platforms and how the performance is affected in each case. Which platform is reliable if employed in aerospace systems?

- What are multitasking systems?

- Running multiple tasks on a single CPU system with Task preemption. Here we learn about implementing a system employing a Hybrid scheduler. We also explore why a commercial RTOS may not be a good choice in systems where there are tight timing constraints.

- What is Priority Inversion and how to avoid it using Hybrid schedulers?

- What are distributed systems and their interconnection topologies?

- How are tasks running on different nodes synchronized in distributed systems?

- CAN protocol and its use in distributed systems.

Mode of assessment for CERTIFICATION

- Closed book exam with university-style conditions.

- 12 Planned Exercises that would be submitted by candidates during the course. The exercises are critical in refining the skills learnt during the course.

Certification

- On successful completion of the course candidates will receive LEVEL 1 internationally recognized Certification from SafeTTy Systems.

Course Duration and Delivery

- Course duration is 8 weeks.

- Course lectures will be held once a week for 4 hours with 2 hours of theory and 2 hours of practical’s.

- Candidates are expected to complete the 12 exercises by the 12th week, before the written exam.

- Final written examination of 2 hours duration would be held at the end of the 15th week since the start of the course.

- Successful candidates will receive SafeTTy Certified certificates within 5 months from the start of the course.

Course Name: Level-2 Engineering of Reliable Embedded Systems(TTb)

Course Location: On-Campus

Course delivery: Face-to-face on-campus delivered by Dr. Michael J. Pont.

Course Duration: 5 days (1 seminar every day for 3 hours followed by practical session for the rest of the day). Final written Exam will be conducted 12-weeks after the course completion.

Hardware board to be used: As per the institution’s requirement. Board to be provided to the candidates by the institution. The details of the hardware board to be used should be shared with us 2-months prior to the course commencement date so as to customise the software for the selected board.

Batch Size: Ideally 20 candidates per batch with a maximum of 50 candidates per batch. Batch size to be confirmed a week in advance before the commencement of the course.

Who will be the Course participants: Level-1 certified candidates.

Other candidates need to provide CV and relevant industry experience details 15-days in advance so that we can assess their suitability for this course in order that they can complete the course comfortably considering the intensiveness of the course.

Certification: 70% pass score in the 2-hour university style written examination conducted at the end of 12-weeks. Successful candidates receive Level-2 SafeTTy Certified certification within 2-months of successful course completion.

Benefits for the course participants: Course delivered on-campus. Internationally designed Courseware which is the copyright of SafeTTy Systems(UK) designed by Dr. Michael J. Pont. Course focuses on the design aspects with Time Triggered architecture and not Event Triggered(Interrupt driven) architecture which is generally followed in engineering courses. Internationally recognized Certificate will be awarded to successful candidates at the end of the course. Course focuses on CPU schedulers and international safety standards in different domains.International Certificate for Level-2 from SafeTTy Systems.

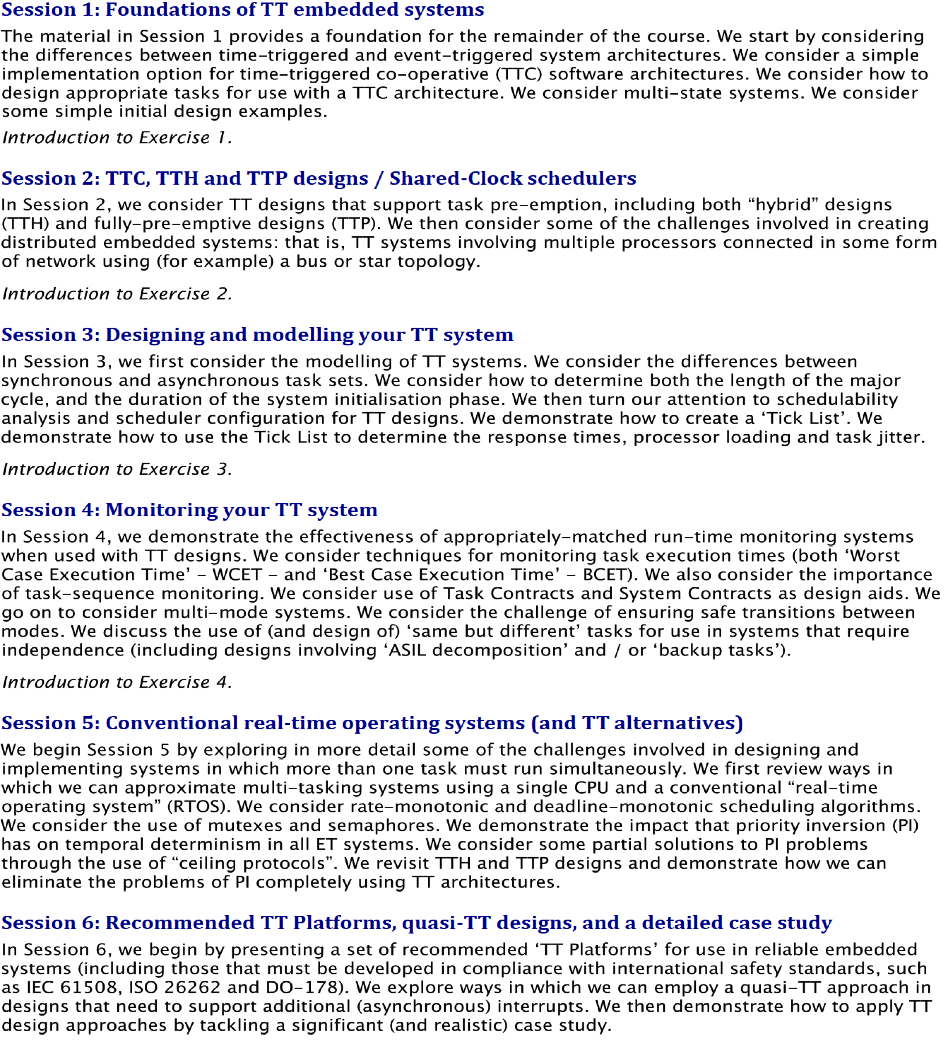

Detailed syllabus is available below.